# CSCI-2500: Computer Organization

Boolean Logic & Arithmetic for Computers (Chapter 3 and App. B)

# Boolean Algebra

- Developed by George Boole in the 1850s

- Mathematical theory of logic.

Shannon was the first to use Boolean Algebra to solve problems in electronic circuit design. (1938)

## Variables & Operations

- All variables have the values 1 or 0

- sometimes we call the values TRUE / FALSE

- Three operators:

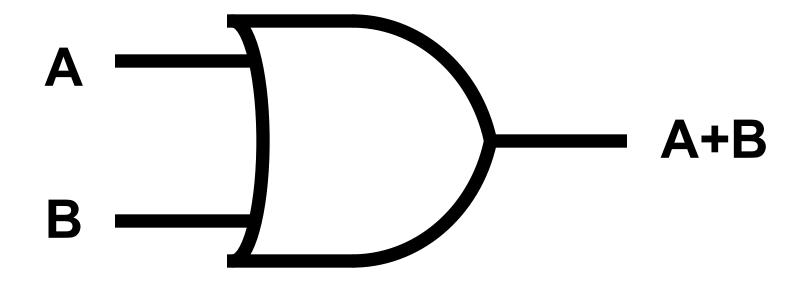

- OR written as +, as in A + B

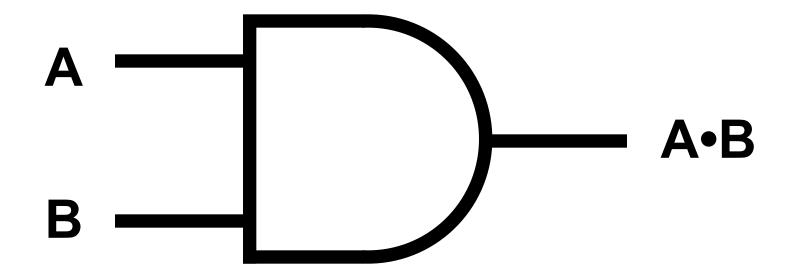

- AND written as •, as in  $A \cdot B$

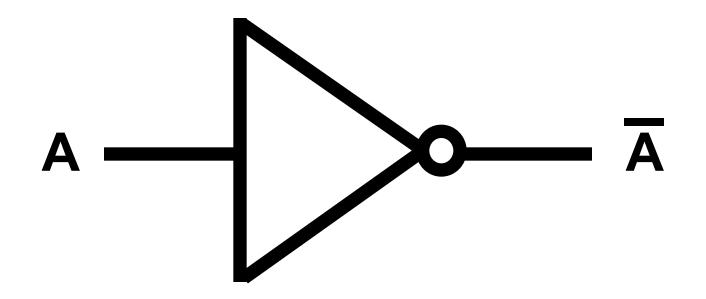

- NOT written as an overline, as in A

## **Operators: OR**

- The result of the OR operator is 1 if either of the operands is a 1.

- The only time the result of an OR is 0 is when both operands are 0s.

- OR is like our old pal addition, but operates only on binary values.

## **Operators:** AND

- The result of an AND is a 1 only when both operands are 1s.

- If either operand is a 0, the result is 0.

AND is like our old nemesis multiplication, but operates on binary values.

## **Operators: NOT**

NOT is a *unary* operator - it operates on only one operand.

- NOT *negates* its operand.

- If the operand is a 1, the result of the NOT is a 0.

## Equations

Boolean algebra uses equations to express relationships. For example:

$$X = A \cdot (\overline{B} + C)$$

This equation expressed a relationship between the value of X and the values of A, B and C.

#### What is the value of each X:

$$X_{1} = 1 \cdot (0 + 1)$$

$$X_{2} = A + \overline{A}$$

$$X_{3} = A \cdot \overline{A}$$

$$X_{4} = X_{4} + 1 \quad \leftarrow \text{huh?}$$

## Laws of Boolean Algebra

Just like in *good old algebra*, Boolean Algebra has postulates and identities.

We can often use these laws to reduce expressions or put expressions in to a more desirable form.

## **Basic Postulates of Boolean Algebra**

Using just the basic postulates – everything else can be derived. Commutative laws Distributive laws Identity Inverse

### A + 0 = A

## $A \cdot 1 = A$

# $A + \overline{A} = 1$

# $A \cdot \overline{A} = 0$

**Commutative Laws**

## A + B = B + A

## $A \cdot B = B \cdot A$

**Distributive Laws**

## $A + (B \cdot C) = (A + B) \cdot (A + C)$

## $A \cdot (B + C) = (A \cdot B) + (A \cdot C)$

#### Can be derived from the basic postulates.

#### Laws of Ones and Zeros

Associative Laws

DeMorgan's Theorems

Zero and One Laws

#### A + 1 = 1 Law of Ones

#### $A \cdot 0 = 0$ Law of Zeros

Associative Laws

## A + (B + C) = (A + B) + C

## $A \cdot (B \cdot C) = (A \cdot B) \cdot C$

## DeMorgan's Theorems

# $\overline{A + B} = \overline{A \cdot B}$

# $\overline{A \cdot B} = \overline{A} + \overline{B}$

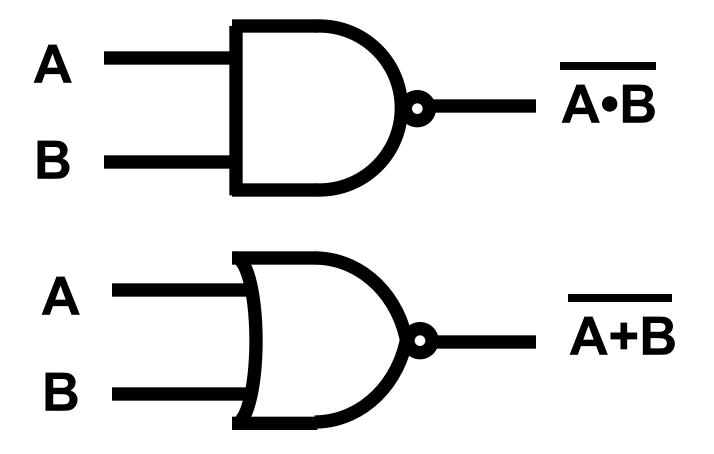

## **Other Operators**

- Boolean Algebra is defined over the 3 operators AND, OR and NOT.

- this is a *functionally complete set*.

- There are other useful operators:

- NOR: is a 0 if either operand is a 1

- NAND: is a 0 only if both operands are 1

- XOR: is a 1 if the operands are different.

- NOTE: NOR or NAND is (by itself) a functionally complete set!

## **Boolean Functions**

- Boolean functions are functions that operate on a number of Boolean variables.

- The result of a Boolean function is itself either a 0 or a 1.

• Example: *f(a,b) = a+b*

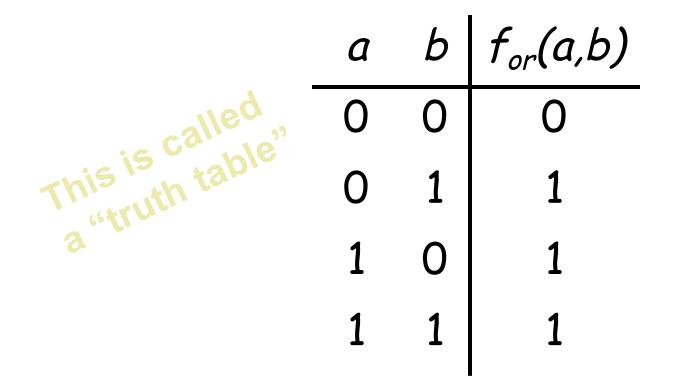

## Alternative Representation

- We can define a Boolean function by showing it using algebraic operations.

- We can also define a Boolean function by listing the value of the function for all possible inputs.

## OR as a Boolean Function $f_{or}(a,b)=a+b$

| а | Ь | OR | AND | NOR | NAN<br>D | XOR |

|---|---|----|-----|-----|----------|-----|

| 0 | 0 | 0  | 0   | 1   | 1        | 0   |

| 0 | 1 | 1  | 0   | 0   | 1        | 1   |

| 1 | 0 | 1  | 0   | 0   | 1        | 1   |

| 1 | 1 | 1  | 1   | 0   | 0        | 0   |

Truth Table for (X+Y)·Z

| Х | У | Ζ | (X+Y)·Z |

|---|---|---|---------|

| 0 | 0 | 0 | 0       |

| 0 | 0 | 1 | 0       |

| 0 | 1 | 0 | 0       |

| 0 | 1 | 1 | 1       |

| 1 | 0 | 0 | 0       |

| 1 | 0 | 1 | 1       |

| 1 | 1 | 0 | 0       |

| 1 | 1 | 1 | 1       |

- Digital logic circuits are electronic circuits that are implementations of some Boolean function(s).

- A circuit is built up of *gates*, each *gate* implements some simple logic function.

# Gates compute something!

- The output depends on the inputs.

- If the input changes, the output might change.

- If the inputs don't change the output does not change.

## An AND gate

## NAND and NOR gates

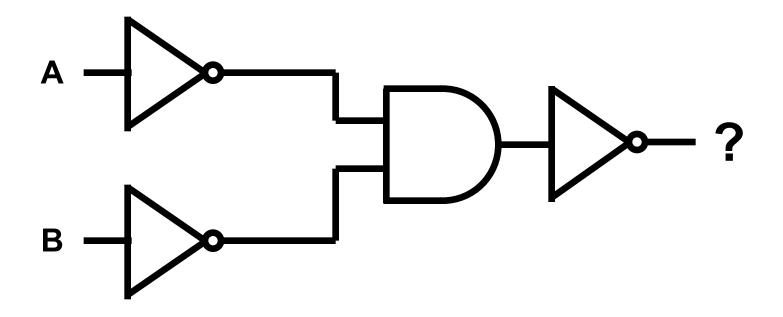

## **Combinational Circuits**

- We can put gates together into circuits

- output from some gates are inputs to others.

- We can design a circuit that represents any Boolean function!

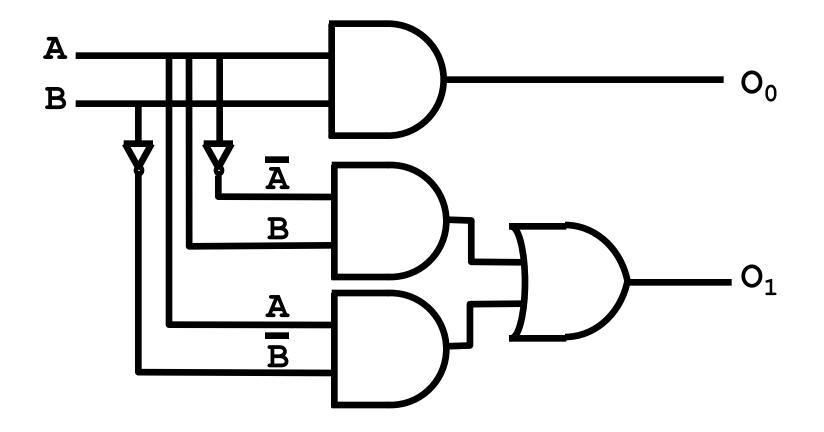

## A Simple Circuit

## Truth Table for our circuit

| а | Ь | a | Ъ | а·Ъ | ā · b |

|---|---|---|---|-----|-------|

| 0 | 0 | 1 | 1 | 1   | 0     |

| 0 | 1 | 1 | 0 | 0   | 1     |

| 1 | 0 | 0 | 1 | 0   | 1     |

| 1 | 1 | 0 | 0 | 0   | 1     |

## Alternative Representations

Any of these can express a Boolean function. :

> Boolean Equation Circuit (Logic Diagram) Truth Table

## Implementation

- A logic diagram is used to design an implementation of a function.

- The implementation is the specific gates and the way they are connected.

- We can buy a bunch of gates, put them together (along with a power source) and build a machine.

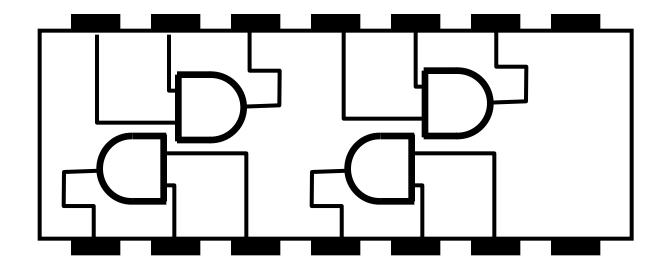

#### **Integrated Circuits**

You can buy an AND gate chip:

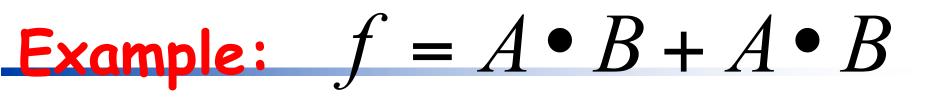

#### **Function Implementation**

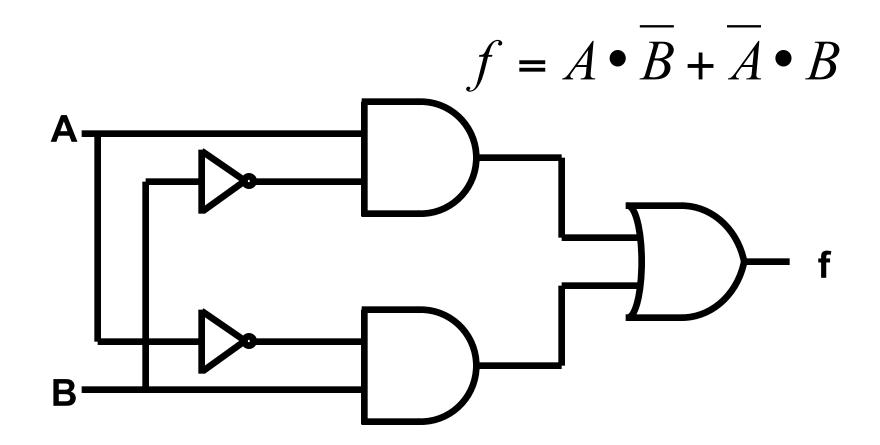

Given a Boolean function expressed as a truth table or Boolean Equation, there are many possible implementations.

The actual implementation depends on what kind of gates are available.

In general we want to minimize the number of gates.

# AB $A \bullet B$ $\overline{A} \bullet B$ f00000010111010111000

#### **One Implementation**

#### Another Implementation

#### Proof it's the same function

$$A \cdot \overline{B} + \overline{A} \cdot B =$$

$$DeMorgan's Law$$

$$\overline{(A \cdot \overline{B})} \cdot \overline{(\overline{A} \cdot B)} =$$

$$DeMorgan's Laws$$

$$\overline{(\overline{A} + B)} \cdot \overline{(A + \overline{B})} =$$

$$Distributive$$

$$\overline{((\overline{A} + B)} \cdot A) + ((\overline{A} + B) \cdot \overline{B}) =$$

$$Distributive$$

$$\overline{(\overline{A} \cdot A + B \cdot A)} + (\overline{A} \cdot \overline{B} + B \cdot \overline{B}) =$$

$$Inverse, Identity$$

$$\overline{(B \cdot A)} + (\overline{A} \cdot \overline{B}) =$$

$$DeMorgan's Laws$$

$$\overline{(B \cdot A)} \cdot (\overline{A} \cdot \overline{B}) =$$

$$DeMorgan's Laws$$

#### **Common Components**

- There are many commonly used components in processor design.

- We will use these components when we design control systems (later).

- We will look at the functionality and design of some of these components now.

#### Some commonly used components

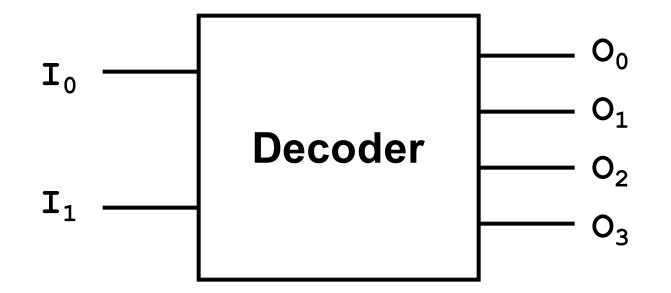

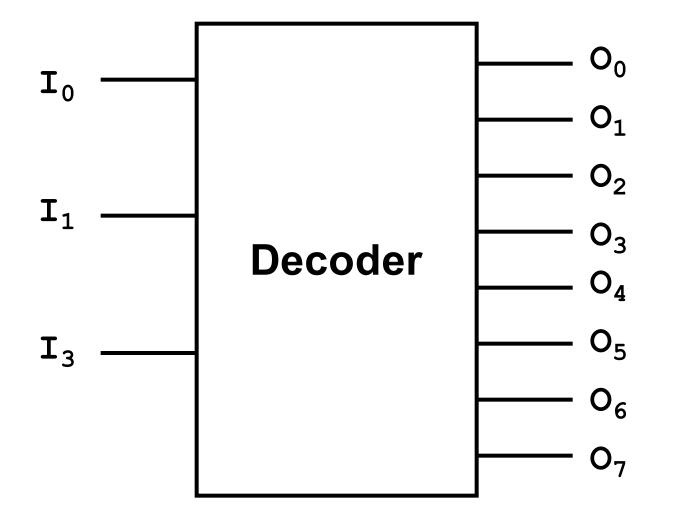

- Decoders: *n* inputs, 2<sup>*n*</sup> outputs.

- the inputs are used to select which output is turned on.

- Multiplexors: 2<sup>n</sup> inputs, n selection bits,

1 output.

- the selection bits determine which input will become the output.

#### 2 input Decoder

#### Decoder Truth Table

| I <sub>0</sub> | $I_1$ | <b>O</b> <sub>0</sub> | <b>O</b> <sub>1</sub> | 0 <sub>2</sub> | 0 <sub>3</sub> |

|----------------|-------|-----------------------|-----------------------|----------------|----------------|

| 0              | 0     | 1                     | 0                     | 0              | 0              |

| 0              | 1     | 0                     | 1                     | 0              | 0              |

| 1              | 0     | 0                     | 0                     | 1              | 0              |

| 1              | 1     | 0                     | 0                     | 0              | 1              |

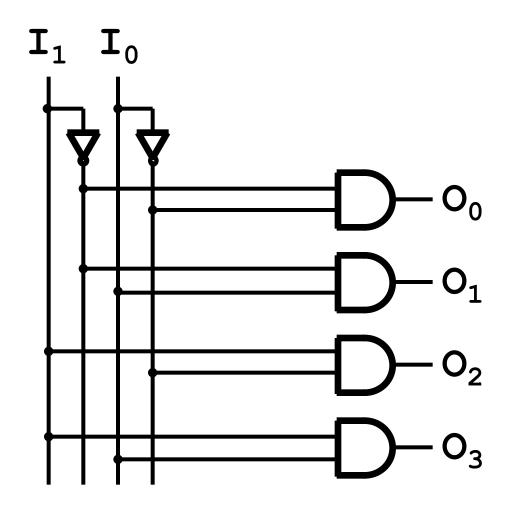

#### **Decoder Boolean Expressions**

## $\mathbf{O}_0 = \mathbf{I}_0 \bullet \mathbf{I}_1$ $\mathbf{O}_1 = \mathbf{I}_0 \bullet \mathbf{I}_1$ $\mathbf{O}_2 = \mathbf{I}_0 \bullet \mathbf{I}_1$ $O_3 = I_0 \bullet I_1$

#### **Decoder Implementation**

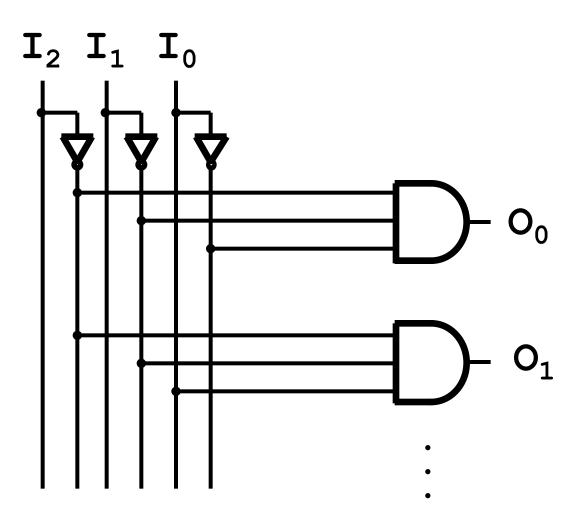

**3 Input Decoder**

#### 3 Input Decoder Truth Table

| $I_2$ | $I_1$ | I <sub>0</sub> | <b>O</b> <sub>0</sub> | 01 | 0 <sub>2</sub> | 0 <sub>3</sub> | O <sub>4</sub> | 0 <sub>5</sub> | 0 <sub>6</sub> | 0 <sub>7</sub> |

|-------|-------|----------------|-----------------------|----|----------------|----------------|----------------|----------------|----------------|----------------|

| 0     |       |                |                       |    | 0              |                |                |                |                |                |

| 0     |       |                |                       |    | 0              |                |                |                |                | 0              |

| 0     | 1     | 0              | 0                     | 0  | 1              | 0              | 0              | 0              | 0              | 0              |

| 0     | 1     | 1              | 0                     | 0  | 0              | 1              | 0              | 0              | 0              | 0              |

| 1     | 0     | 0              |                       | 0  | •              | 0              | 1              | 0              | 0              | 0              |

| 1     | 0     | 1              | 0                     | 0  | 0              | 0              | 0              | 1              | 0              | 0              |

| 1     | 1     | 0              | 0                     | 0  | 0              | 0              | 0              | 0              | 1              | 0              |

| 1     | 1     | 1              | 0                     | 0  | 0              | 0              | 0              | 0              | 0              | 1              |

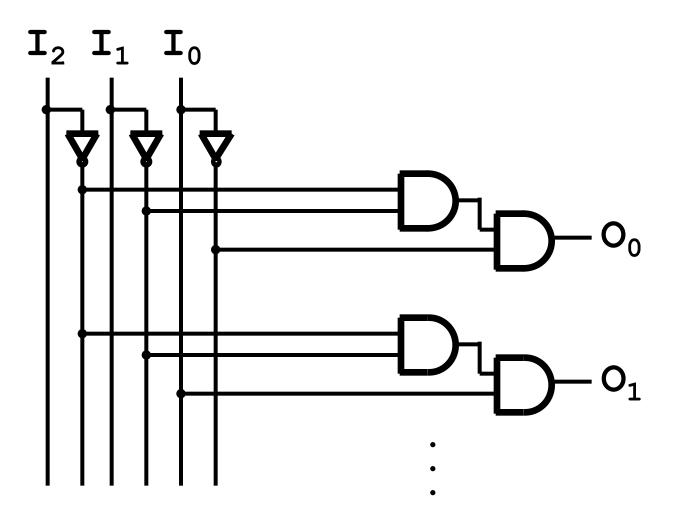

#### **3-Decoder Boolean Expressions**

$$O_{0} = \overline{I_{0}} \bullet \overline{I_{1}} \bullet \overline{I_{2}}$$

$$O_{1} = \overline{I_{2}} \bullet \overline{I_{1}} \bullet I_{0}$$

$$O_{2} = \overline{I_{2}} \bullet I_{1} \bullet \overline{I_{0}}$$

$$O_{3} = \overline{I_{2}} \bullet I_{1} \bullet I_{0}$$

$$O_{4} = I_{2} \bullet \overline{I_{1}} \bullet \overline{I_{0}}$$

$$O_{5} = I_{2} \bullet \overline{I_{1}} \bullet I_{0}$$

$$O_{6} = I_{2} \bullet I_{1} \bullet \overline{I_{0}}$$

$$O_{7} = I_{2} \bullet I_{1} \bullet I_{0}$$

#### **3-Decoder Partial Implementation**

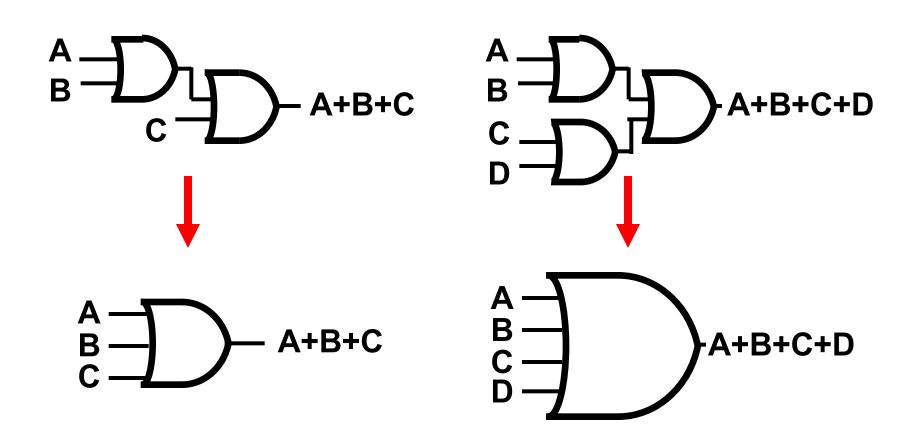

#### A Useful Simplification

The above logic diagram is often abbreviated as shown below:

$$\begin{array}{c} A \\ B \\ C \end{array} - A \cdot B \cdot C$$

We can do this (without possible confusion) because of the associative property.

#### **Revised Partial 3-Decoder**

#### Multiple Input Or Gates

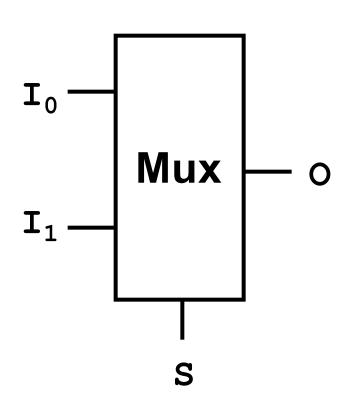

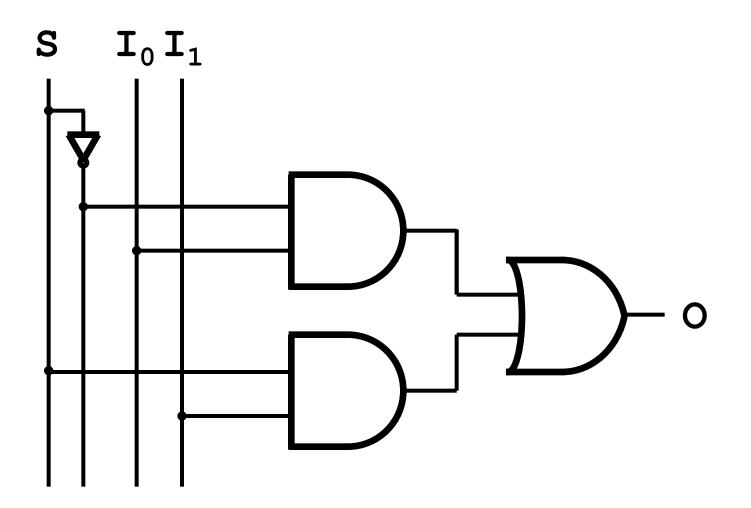

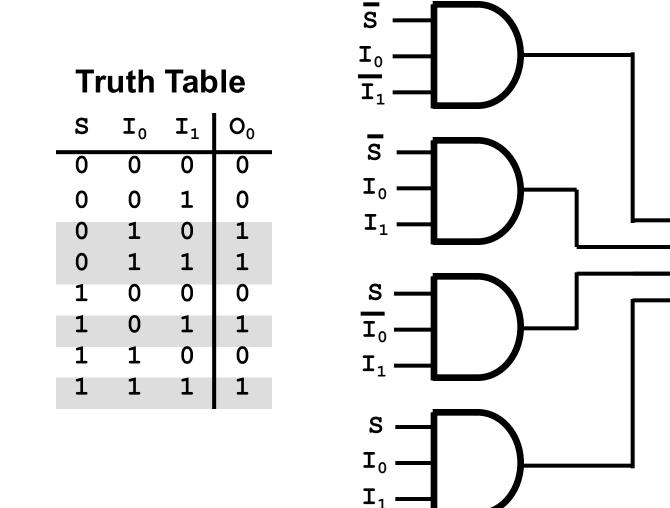

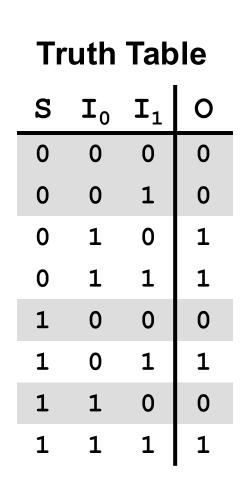

### 2 Input Multiplexor

Inputs:  $I_0$  and  $I_1$ Selector: S Output: O If S is a O:  $O=I_0$ If S is a 1:  $O=I_1$

#### **2-Mux Boolean Function**

- The output depends on  $I_0$  and  $I_1$

- The output also depends on s !!!

• We must treat s as an input.

$$\mathbf{O} = f(\mathbf{I}_0, \mathbf{I}_1, \mathbf{S})$$

2-Mux Truth Table

| Abbreviated<br>Truth Table |     |                |  |  |  |  |

|----------------------------|-----|----------------|--|--|--|--|

|                            | s o |                |  |  |  |  |

|                            | 0   | I <sub>0</sub> |  |  |  |  |

|                            | 1   | $I_1$          |  |  |  |  |

|                            |     |                |  |  |  |  |

| S | I <sub>0</sub> | $I_1$ | <b>O</b> <sub>0</sub> |

|---|----------------|-------|-----------------------|

| 0 | 0              | 0     | 0                     |

| 0 | 0              | 1     | 0                     |

| 0 | 1              | 0     | 1                     |

| 0 | 1              | 1     | 1                     |

| 1 | 0              | 0     | 0                     |

| 1 | 0              | 1     | 1                     |

| 1 | 1              | 0     | 0                     |

| 1 | 1              | 1     | 1                     |

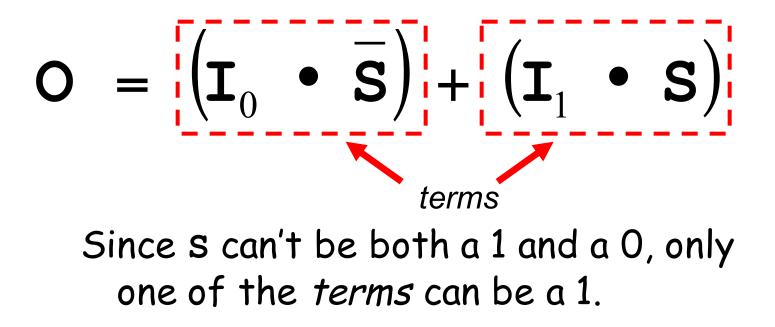

#### **2-Mux Boolean Expression**

2-Mux Logic Design

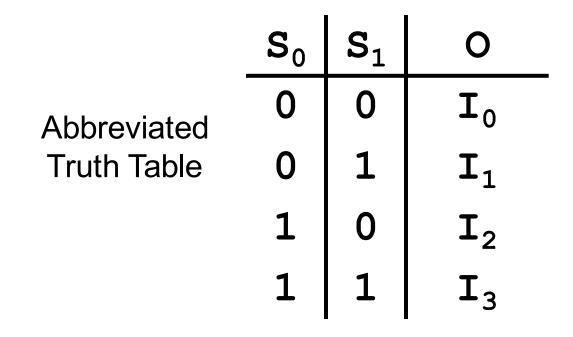

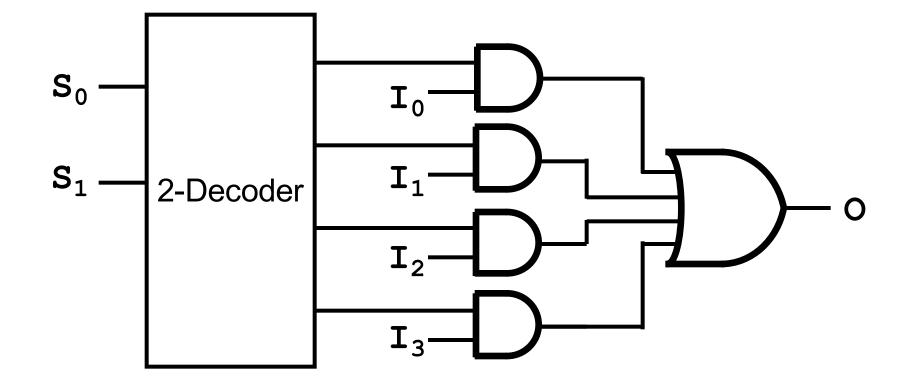

#### 4 Input Multiplexor

• If we have 4 inputs, we need to have 2 selection bits:  $S_0 S_1$

One Possible 4-Mux

#### **Common Implementations**

- There are two general forms that are used in many circuit implementations:

- Product of Sums

- A bunch of ORs leading to a big AND gate

- Sum of Products

- A bunch of ANDs leading to a big OR gate

#### Sum of Products

- Express the function by listing all the combinations of inputs for which the output should be a 1.

- These combinations are rows in the truth table where the function has the value 1.

- Represent each combination with an AND gate.

- OR all the AND gates to generate the output.

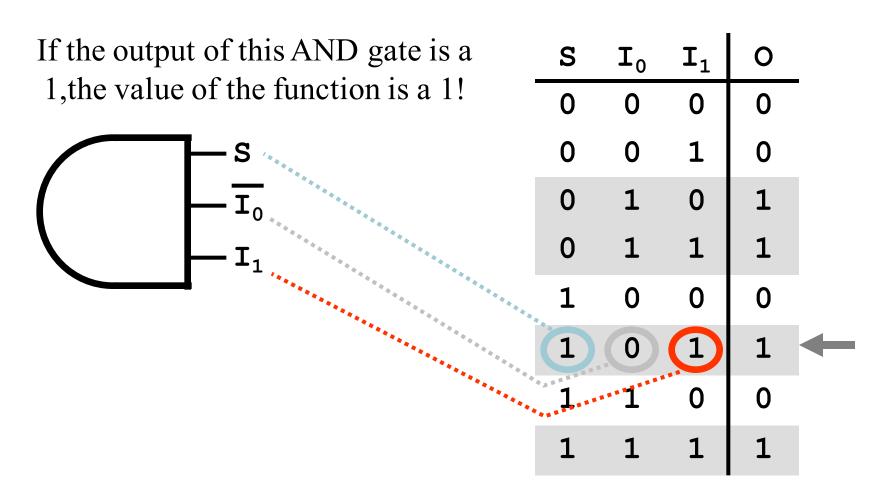

#### SOP Example: 2-Mux

Find rows in truth table where the output is 1.

- If S is 1 in that row, connect s to a 3-input AND gate, otherwise connect S.

- Connect  $I_0$  and  $I_1$  in the same way.

- The AND gate corresponds to the row in the truth table.

| S | I <sub>0</sub> | $I_1$ | 0 |

|---|----------------|-------|---|

| 0 | 0              | 0     | 0 |

| 0 | 0              | 1     | 0 |

| 0 | 1              | 0     | 1 |

| 0 | 1              | 1     | 1 |

| 1 | 0              | 0     | 0 |

| 1 | 0              | 1     | 1 |

| 1 | 1              | 0     | 0 |

| 1 | 1              | 1     | 1 |

#### SOP Example: 2-Mux (cont).

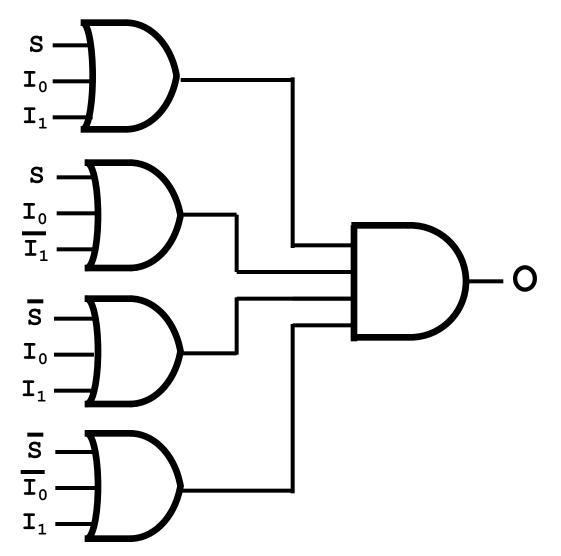

#### **SOP** Construction

- For each row on the truth table that has the value 1 (the function has the value 1) build the corresponding AND gate.

- Ignore all rows where the function has the value O!

- Connect the output of all the AND gates to one big OR gate.

#### 4-Mux Sum Of Products

CSCI-2500 SPRING 2016, Boolean Logic

$\bigcirc$

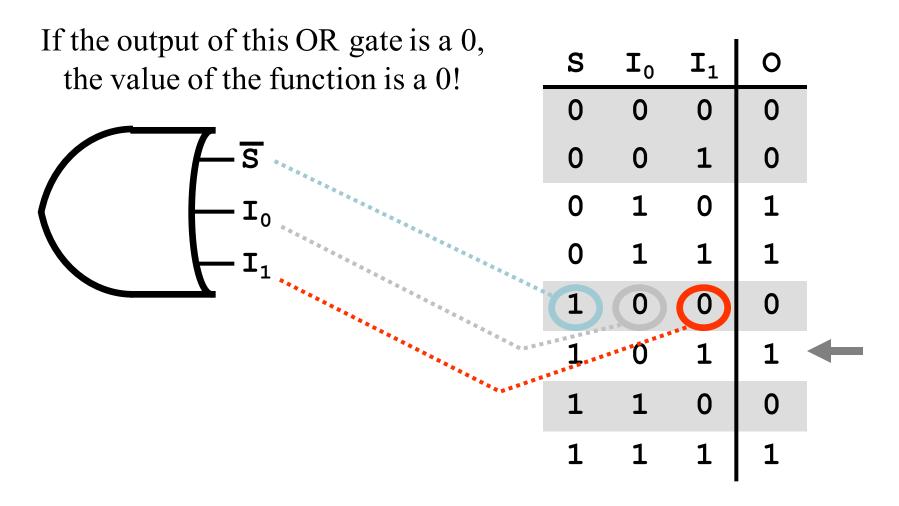

#### **Product of Sums**

- Express the function by listing all the combinations of inputs for which the output should be a 0.

- These combinations are rows in the truth table where the function has the value 0.

- Represent each combination with an OR gate.

- AND all the OR gates to generate the output.

#### POS Example: 2-Mux

Find rows in truth table where the output is 0.

- If S is 0 in that row, connect 3 to a 3-input OR gate, otherwise connect S.

- Connect  $I_0$  and  $I_1$  in the same way.

- The OR gate corresponds to the row in the truth table.

| S | I <sub>0</sub> | $I_1$ | 0 |

|---|----------------|-------|---|

| 0 | 0              | 0     | 0 |

| 0 | 0              | 1     | 0 |

| 0 | 1              | 0     | 1 |

| 0 | 1              | 1     | 1 |

| 1 | 0              | 0     | 0 |

| 1 | 0              | 1     | 1 |

| 1 | 1              | 0     | 0 |

| 1 | 1              | 1     | 1 |

POS Example: 2-Mux (cont).

#### **POS** Construction

- For each row on the truth table that has the value 0 (the function has the value 0) build the corresponding OR gate.

- Ignore all rows where the function has the value 1!

- Connect the output of all the OR gates to one big AND gate.

#### 4-Mux Product of Sums

### Minimization

- SOP and POS forms provide a simple translation from truth table to circuit.

- The resulting designs may involve more gates than are necessary.

- There are a number of techniques used to minimize such circuits.

# **Minimization Techniques**

- Boolean Algebra

- use postulates and identities to reduce expressions.

- Karnaugh Maps

- graphical technique useful for small circuits (no more than 4 or 5 inputs)

- Tabular Methods

- suitable for large functions usually done by a computer program.

# Karnaugh Map (K-map)

- Based on SOP form.

- It may be possible to *merge* terms.

- Example:  $f = (A \cdot B \cdot C) + (\overline{A} \cdot B \cdot C)$

- Close inspection reveals that it doesn't matter what the value of A is!

- Here is a simpler version of the same function:

$$f = (B \bullet C)$$

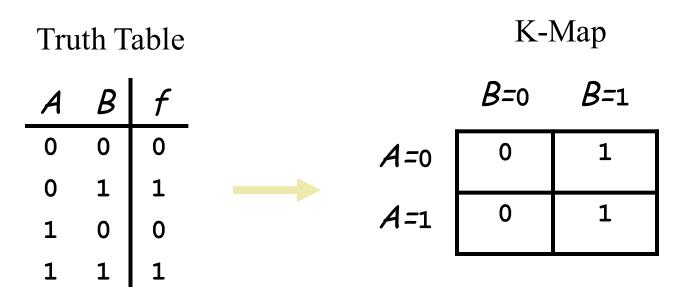

# **Graphical Representation**

- The idea is to draw a picture in which it will be easy to see when *terms* can be merged.

- We draw the truth table in 2-D, the result is similar to a Venn Diagram

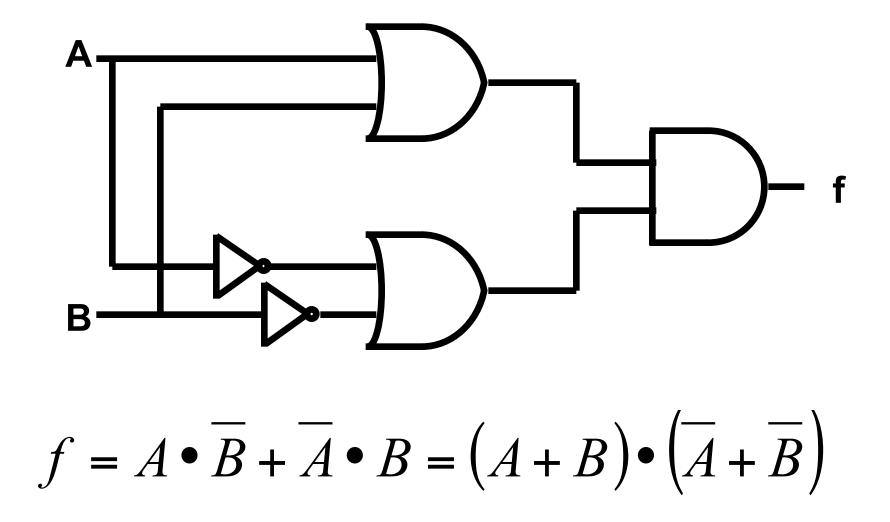

### K-Map Example

$$f = A \bullet B + A \bullet B$$

In the K-Map it's easy to see that the value of A doesn't matter

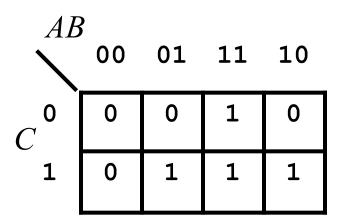

# Ex 2: The Majority Function

- The majority function is 1 whenever the majority of the inputs are 1.

- Here is an SOP Boolean equation for the 3-input majority function:

$$f = A \bullet B \bullet C + \overline{A} \bullet B \bullet C + A \bullet \overline{B} \bullet C + A \bullet B \bullet \overline{C}$$

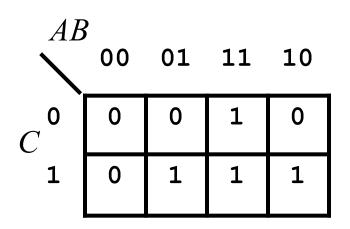

# **K-Map for Majority Function**

#### Truth Table

| A | В | С | f |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

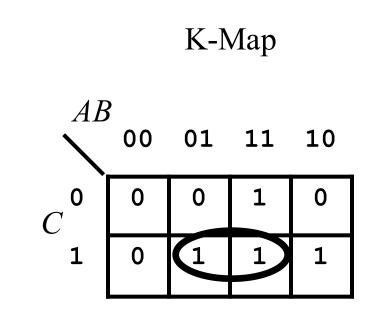

K-Map

## **K-Map** Construction

- Notice that any 2 adjacent cells differ by exactly one bit in the input.

- either A is different, or

B is different or C is

different.

- Never more then 1 variable is different!

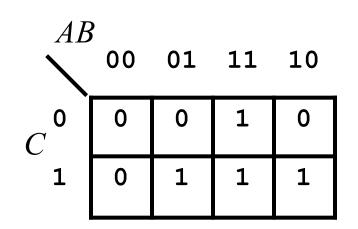

How to use K-Map

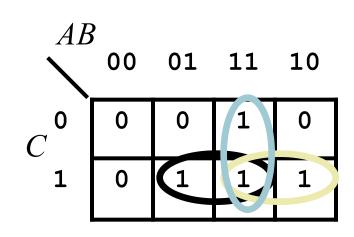

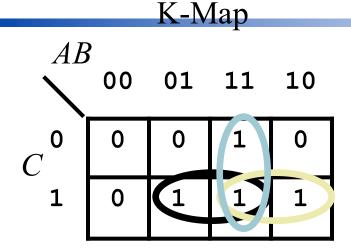

K-Map

Rectangular collections of cells that all have the value 1 indicate it is possible to *merge* the corresponding terms in SOP expression.

The number of cells in the rectangle must be a power of 2!

## **Possible Mergings**

K-Map

There are 3 possible mergings of terms in this K-Map.

## One of the merges

The merge shown means "if C is 1 and B is 1, it doesn't matter what the value of A is"

$$A \bullet B \bullet C + A \bullet B \bullet C = B \bullet C$$

### All 3 reductions

Original:  $f = A \bullet B \bullet C + \overline{A} \bullet B \bullet C + A \bullet \overline{B} \bullet C + A \bullet B \bullet \overline{C}$

Reduced:  $f = B \bullet C + A \bullet C + A \bullet B$

## K-Map Concept

- A professional Logic Designer would need to use minimization techniques every day.

- We are just amateurs, so all we need to know is the general idea.

- that there are systematic procedures for minimizing SOP and POS form Boolean equations.

## Combinational vs. Sequential

- Combinational: output depends completely on the value of the inputs.

- time doesn't matter.

- Sequential: output also depends on the state a little while ago.

- can depend on the value of the output some time in the past.

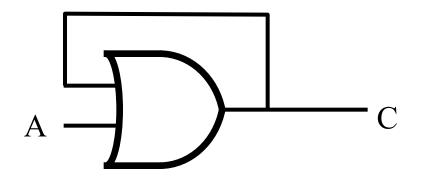

# Memory

- Think about how you might design a combinational circuit that could be used as a single bit *memory*.

- Use your *memory* to recall that the output of a gate can change whenever the inputs change.

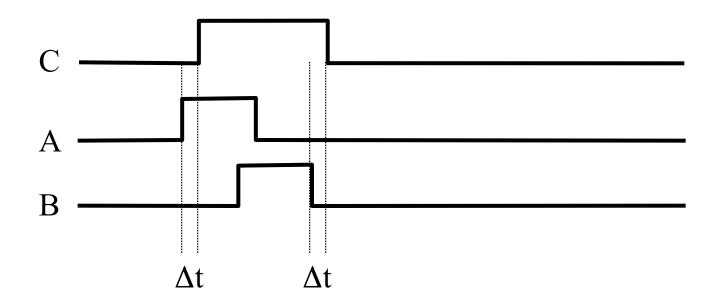

What happens when A changes from 1 to 0?

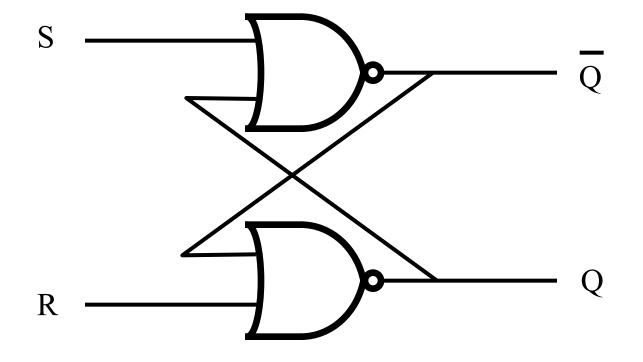

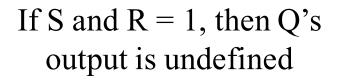

#### S-R latch

| A | В | A nor B |

|---|---|---------|

| 0 | 0 | 1       |

| 0 | 1 | 0       |

| 1 | 0 | 0       |

| 1 | 1 | 0       |

#### S-R latch Truth Table

| $Q_{t}$ | ${f S}_{t}$ | $R_t$ | $Q_{t+1}$ |

|---------|-------------|-------|-----------|

| 0       | 0           | 0     | 0         |

| 0       | 0           | 1     | 0         |

| 0       | 1           | 0     | 1         |

| 0       | 1           | 1     | 0?        |

| 1       | 0           | 0     | 1         |

| 1       | 0           | 1     | 0         |

| 1       | 1           | 0     | 1         |

| 1       | 1           | 1     | 0?        |

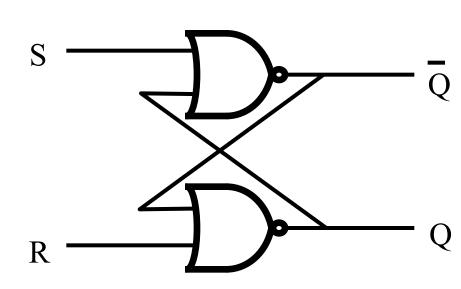

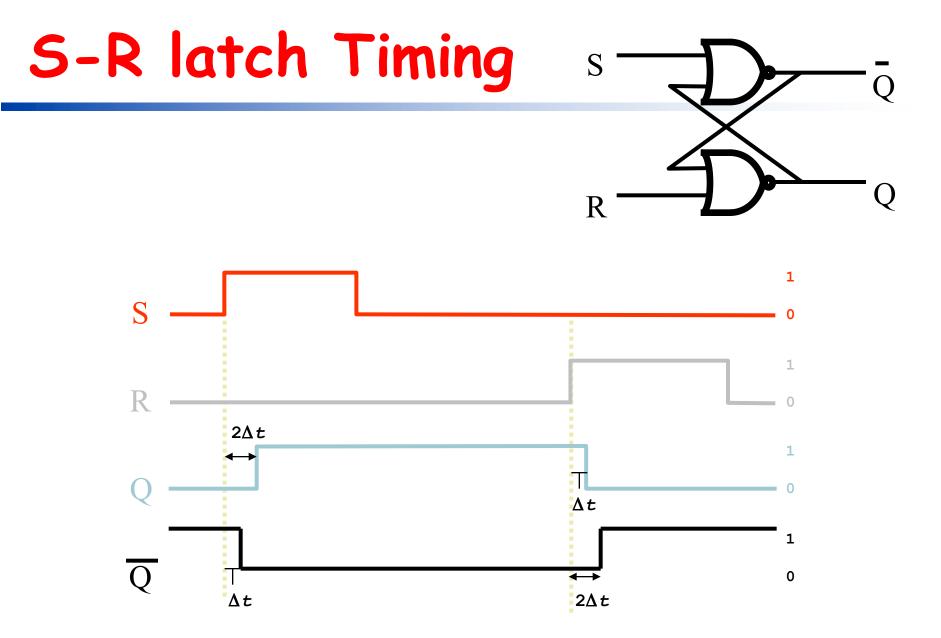

#### Clocked S-R Latch

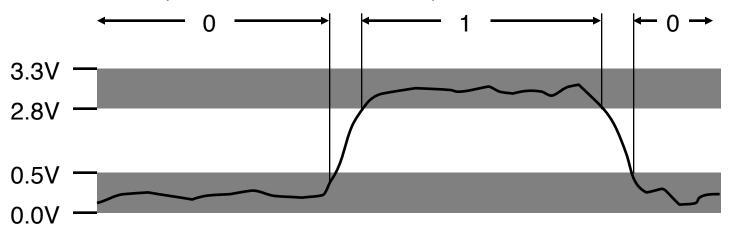

Inside a computer we want the output of gates to change only at specific times.

We can add some circuitry to make sure that changes occur only when a *clock* changes (when the clock changes from 0 to 1).

#### **Clocked S-R Latch**

- Q only changes when the Clock is a 1.

- If Clock is 0, neither S or R *reach* the NOR gates.

### What if S=R=1?

- The truth table shows ? when S=R=1.

- The value of Q is undetermined.

- The circuit is not *stable*.

- We can make sure that S=R !=1 now that we have a clock.

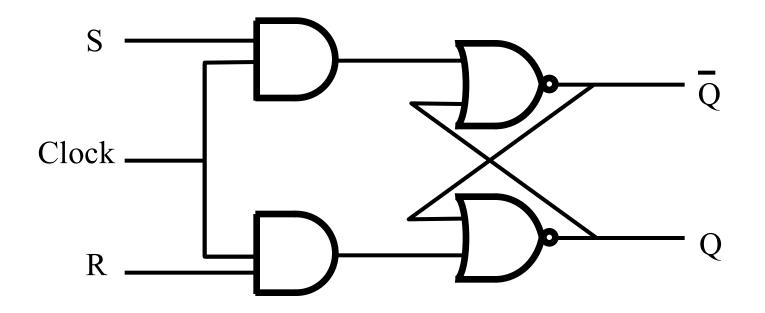

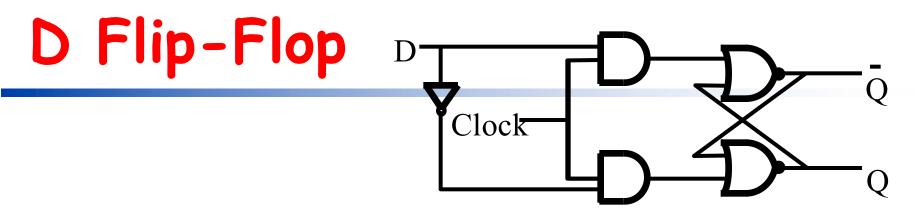

# Avoiding S=R=1: D Flip-Flop

• Now have only one input: D.

• If D is a 1 when the clock becomes 1, the circuit will *remember* the value 1 (Q=1).

• If D is a 0 when the clock becomes 1, the circuit will *remember* the value 0 (Q=0).

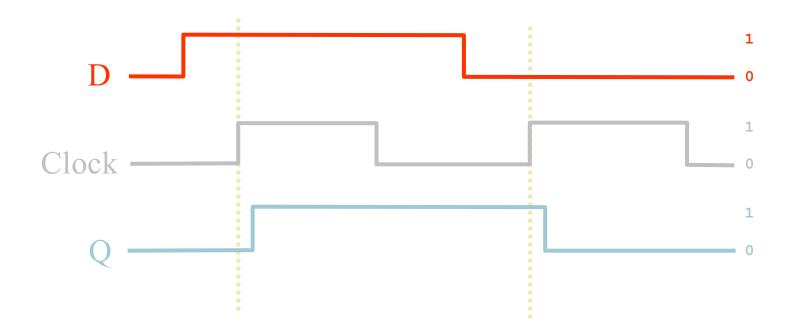

## **D** Flip-Flop Timing

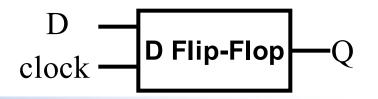

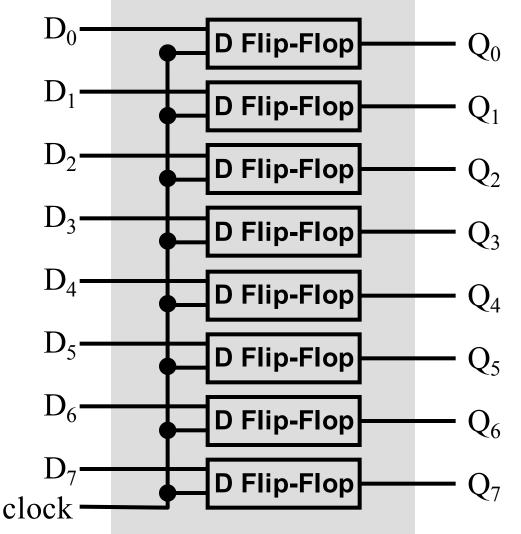

# 8 Bit Memory

We can use 8 D Flip-Flops to create an 8 bit memory.

- We have 8 inputs that we want to store, all are written at the same time.

- all 8 flip-flops use the same clock.

# Bits, Bytes & Words

#### Why Don't Computers Use Base 10?

- Base 10 Number Representation

- That's why fingers are known as "digits"

- Natural representation for financial transactions

- Floating point number cannot exactly represent \$1.20

- Even carries through in scientific notation

- 1.5213 X 10<sup>4</sup>

- Implementing Electronically

- Hard to store

- ENIAC (First electronic computer) used 10 vacuum tubes / digit

- Hard to transmit

- Need high precision to encode 10 signal levels on single wire

- Messy to implement digital logic functions

- Addition, multiplication, etc.

# **Binary Representations**

- Base 2 Number Representation

- Represent 15213<sub>10</sub> as 11101101101101<sub>2</sub>

- Represent 1.20<sub>10</sub> as 1.001100110011[0011]...2

- Represent 1.5213 X 10<sup>4</sup> as 1.1101101101101<sub>2</sub> X 2<sup>13</sup>

- Electronic Implementation

- Easy to store with bistable elements

- Reliably transmitted on noisy and inaccurate wires

• Straightforward implementation of arithmetic functions

#### **Byte-Oriented Memory Organization**

- Programs Refer to Virtual Addresses

- Conceptually very large array of bytes

- Actually implemented with hierarchy of different memory types

- · SRAM, DRAM, disk

- Only allocate for regions actually used by program

- In Unix and Windows NT, address space private to particular "process"

- Program being executed

- Program can clobber its own data, but not that of others

- Compiler + Run-Time System Control Allocation

- Where different program objects should be stored

- Multiple mechanisms: static, stack, and heap

- In any case, all allocation within single virtual address space

# **Encoding Byte Values**

- Byte = 8 bits

- Binary 00000002 to 11111112

- Decimal:  $O_{10}$  to  $255_{10}$

- Hexadecimal  $OO_{16}$  to  $FF_{16}$

- · Base 16 number representation

- Use characters '0' to '9' and 'A' to 'F'

- Write FA1D37B<sub>16</sub> in C as  $0 \times FA1D37B$

- Or 0xfald37b

| Het | •   | mal | 3 |

|-----|-----|-----|---|

| Het | Dec | Bin | 9 |

| 0           | 0      | 0000 |

|-------------|--------|------|

| 1           | 1      | 0001 |

| 1<br>2<br>3 | 2<br>3 | 0010 |

| 3           | 3      | 0011 |

| 4           | 4      | 0100 |

| 5           | 5      | 0101 |

| 6           | 6      | 0110 |

| 7           | 7      | 0111 |

| 8           | 8      | 1000 |

| 9           | 9      | 1001 |

| A           | 10     | 1010 |

| В           | 11     | 1011 |

| С           | 12     | 1100 |

| D           | 13     | 1101 |

| E           | 14     | 1110 |

| F           | 15     | 1111 |

## Machine Words

- Machine Has "Word Size"

- Nominal size of integer-valued data

- Including addresses

- Most current machines are 32 bits (4 bytes)

- Limits addresses to 4GB

- Becoming too small for memory-intensive applications

- High-end systems are 64 bits (8 bytes)

- Potentially address  $\approx 1.8 \times 10^{19}$  bytes

- Machines support multiple data formats

- · Fractions or multiples of word size

- Always integral number of bytes

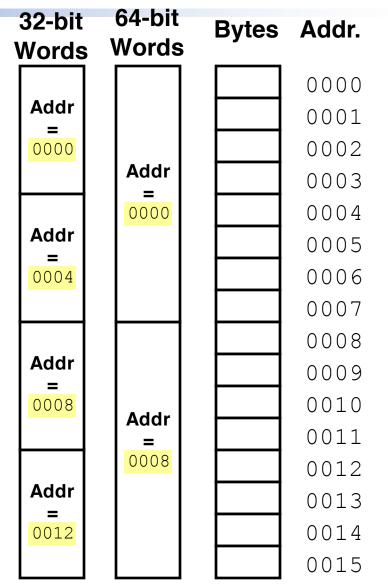

#### Word-Oriented Memory Organization

- Addresses Specify

Byte Locations

- Address of first byte in word

- Addresses of successive words differ by 4 (32-bit) or 8 (64-bit)

### **Data Representations**

- Sizes of C Objects (in Bytes)

- C Data TypeCompaq AlphaTypical 32-bit Intel IA32

| • int                           | 4 | 4 | 4     |

|---------------------------------|---|---|-------|

| <ul> <li>long int</li> </ul>    | 8 | 4 | 4     |

| • char                          | 1 | 1 | 1     |

| <ul> <li>short</li> </ul>       | 2 | 2 | 2     |

| • float                         | 4 | 4 | 4     |

| <ul> <li>double</li> </ul>      | 8 | 8 | 8     |

| <ul> <li>long double</li> </ul> | 8 | 8 | 10/12 |

| • char *                        | 8 | 4 | 4     |

|                                 | • |   |       |

• Or any other pointer

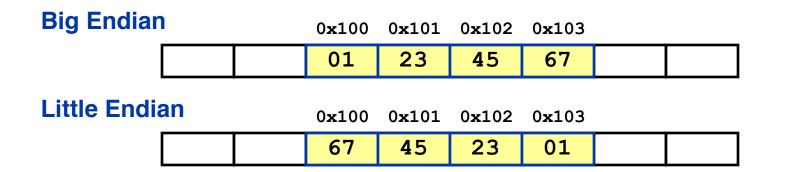

## Byte Ordering

- How should bytes within multi-byte word be ordered in memory?

- Conventions

- Sun's, Mac's are "Big Endian" machines

- Least significant byte has highest address

- Alphas, PC's are "Little Endian" machines

- Least significant byte has lowest address

## Byte Ordering Example

- Big Endian

- Least significant byte has highest address

- Little Endian

- Least significant byte has lowest address

- Example

- Variable x has 4-byte representation 0x01234567

- Address given by &x is 0x100

# **Reading Byte-Reversed Listings**

- Disassembly

- Text representation of binary machine code

- Generated by program that reads the machine code

- Example Fragment

| Address<br>8048365:<br>8048366:<br>804836c: | Instruction Cod         5b         81 c3 ab 12 (         83 bb 28 00 ( | 00 00 | Assem<br>pop<br>add<br>cmpl | bly Rendition<br>%ebx<br>\$0x12ab,%ebx<br>\$0x0,0x28(%ebx) |

|---------------------------------------------|------------------------------------------------------------------------|-------|-----------------------------|------------------------------------------------------------|

| •                                           | ring Numbers                                                           |       |                             |                                                            |

| <ul> <li>Value:</li> </ul>                  |                                                                        | (     | )x12ab                      |                                                            |

| <ul> <li>Pad to</li> </ul>                  | 4 bytes:                                                               | 0x000 | )012ab                      |                                                            |

| • Split                                     | into bytes:                                                            | 00 00 | 12 ab                       |                                                            |

| <ul> <li>Rever</li> </ul>                   | se:                                                                    | ab 12 | 00 00<br>csci-2             | 500 SPRING 2016, Boolean Logi                              |

#### **Examining Data Representations**

- Code to Print Byte Representation of Data

- Casting pointer to unsigned char \* creates byte array

```

typedef unsigned char *pointer;

void show_bytes(pointer start, int len)

{

int i;

for (i = 0; i < len; i++)

printf("0x%p\t0x%.2x\n",

start+i, start[i]);

printf("\n");

}

```

**Printf directives:**

%p: Print pointer

**%x: Print Hexadecimal**

### show\_bytes Execution Example

```

int a = 15213;

printf("int a = 15213;\n");

show bytes((pointer) &a, sizeof(int));

```

#### **Result (Linux):**

| int a = 15213 | 3;   |

|---------------|------|

| 0x11ffffcb8   | 0x6d |

| 0x11ffffcb9   | 0x3b |

| 0x11ffffcba   | 0x00 |

| 0x11ffffcbb   | 0x00 |

| 4             |      |

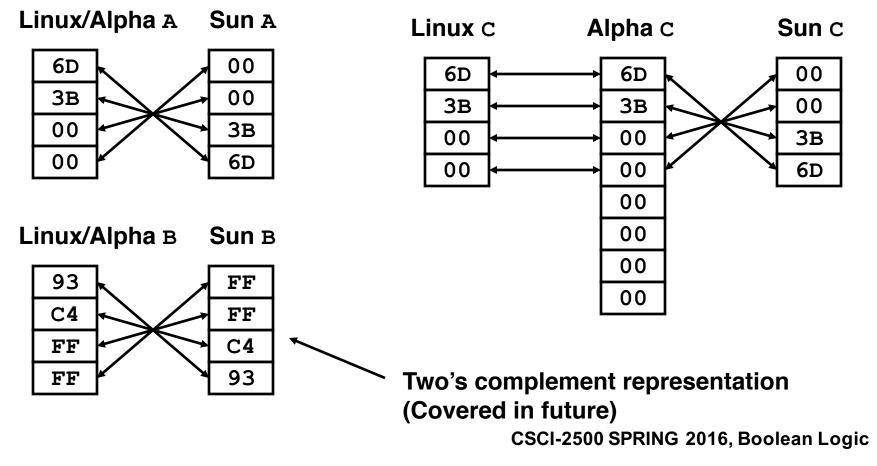

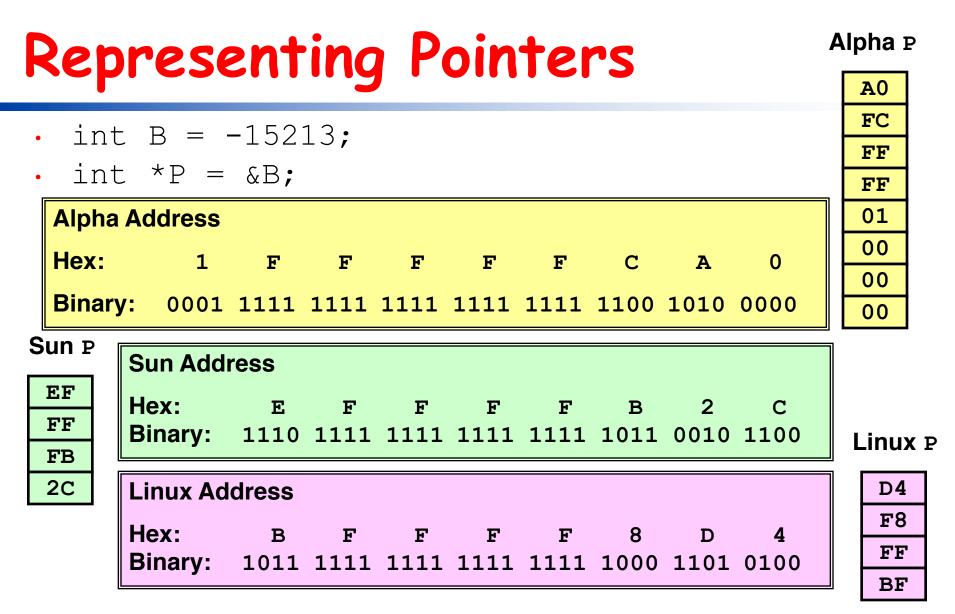

## **Representing Integers**

- int A = 15213;

- int B = -15213;

- long int C = 15213;

| Decimal: | 15213 |      |      |      |

|----------|-------|------|------|------|

| Binary:  | 0011  | 1011 | 0110 | 1101 |

| Hex:     | 3     | В    | 6    | D    |

Different compilers & machines assign different locations to objects

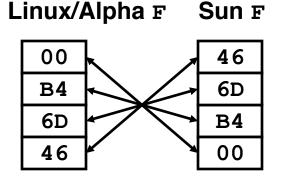

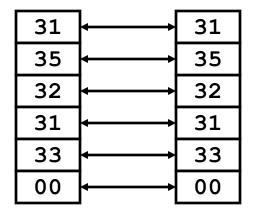

## **Representing Floats**

• Float F = 15213.0;

Not same as integer representation, but consistent across machines Can see some relation to integer representation, but not obvious CSCI-2500 SPRING 2016, Boolean Logic

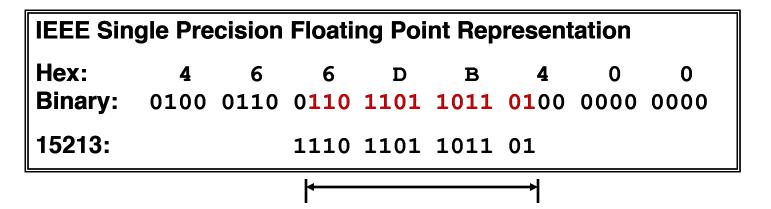

## **Representing Strings**

- Strings in C

- Represented by array of characters

- Each character encoded in ASCII format

- · Standard 7-bit encoding of character set

- Other encodings exist, but uncommon

- Character "O" has code 0x30

- Digit *i* has code 0x30+*i*

- String should be null-terminated

- Final character = 0

- Compatibility

- Byte ordering not an issue

- · Data are single byte quantities

- Text files generally platform independent

- Except for different conventions of line termination character(s)!

- char S[6] =

- "15213";

- Linux/Alpha s Sun s

#### Machine-Level Code Representation

- Encode Program as Sequence of Instructions

- Each simple operation

- Arithmetic operation

- Read or write memory

- · Conditional branch

- Instructions encoded as bytes

- · Alpha's, Sun's, Mac's use 4 byte instructions

- Reduced Instruction Set Computer (RISC)

- PC's use variable length instructions

- Complex Instruction Set Computer (CISC)

- Different instruction types and encodings for different machines

- Most code not binary compatible

- Programs are Byte Sequences Too!

## **Representing Instructions**

- int sum(int x, int y)

- {

- return x+y;

- For this example, Alpha & Sun use two 4-byte instructions

- Use differing numbers of instructions in other cases

- PC uses 7 instructions with lengths 1, 2, and 3 bytes

- Same for NT and for Linux

- NT / Linux not fully binary compatible

Different machines use totally different instructions and encodings

CSCI-2500 SPRING 2016, Boolean Logic

| Alpha sur |    |  |  |

|-----------|----|--|--|

|           | 00 |  |  |

|           | 00 |  |  |

|           | 30 |  |  |

|           | 42 |  |  |

|           | 01 |  |  |

|           | 80 |  |  |

|           | FA |  |  |

|           | 6B |  |  |

|           |    |  |  |

| m S | Sun sum |  |  |

|-----|---------|--|--|

|     | 81      |  |  |

|     | C3      |  |  |

|     | E0      |  |  |

|     | 08      |  |  |

|     | 90      |  |  |

|     | 02      |  |  |

|     | 00      |  |  |

|     | 09      |  |  |

|     |         |  |  |

PC sum

| 55 |

|----|

| 89 |

| E5 |

| 8B |

| 45 |

| 0C |

| 03 |

| 45 |

| 08 |

| 89 |

| EC |

| 5D |

| C3 |

|    |

#### Bit-Level Operations in C

- Operations &, |, ~, ^ Available in C

- Apply to any "integral" data type

- long, int, short, char

- View arguments as bit vectors

- · Arguments applied bit-wise

- Examples (Char data type)

- ~0x41 --> 0xBE ~01000001<sub>2</sub> --> 10111110<sub>2</sub>

- ~0x00 --> 0xFF ~0000000<sub>2</sub> --> 1111111<sub>2</sub>

- 0x69 & 0x55 --> 0x41 01101001<sub>2</sub> & 01010101<sub>2</sub> --> 01000001<sub>2</sub>

- 0x69 | 0x55 --> 0x7D 01101001<sub>2</sub> | 01010101<sub>2</sub> --> 01111101<sub>2</sub>

#### Contrast: Logic Operations in C

- Contrast to Logical Operators

- & & , | |, !

- View 0 as "False"

- Anything nonzero as "True"

- · Always return 0 or 1

- Early termination

- Examples (char data type)

- !0x41 --> 0x00

- !0x00 --> 0x01

- !!0x41 --> 0x01

- 0x69 && 0x55 --> 0x01

- 0x69 || 0x55 --> 0x01

- p && \*p (avoids null pointer access)

## Shift Operations

- Left Shift: x << y

- Shift bit-vector  $\mathbf x$  left  $\mathbf y$  positions

- . Throw away extra bits on left

- Fill with O's on right

- Right Shift: x >> y

- Shift bit-vector  $\mathbf x$  right  $\mathbf y$  positions

- . Throw away extra bits on right

- Logical shift

- · Fill with O's on left

- Arithmetic shift

- Replicate most significant bit on right

- Useful with two's complement integer representation

| Argument x  | 01100010         |  |

|-------------|------------------|--|

| << 3        | 00010 <i>000</i> |  |

| Log. >> 2   | <i>00</i> 011000 |  |

| Arith. >> 2 | <i>00</i> 011000 |  |

| Argument x  | 10100010         |

|-------------|------------------|

| << 3        | 00010 <i>000</i> |

| Log. >> 2   | <i>00</i> 101000 |

| Arith. >> 2 | <i>11</i> 101000 |

### **Cool Stuff with Xor**

- Bitwise Xor is form of addition

- With extra property that every value is its own additive inverse

$A^{A} = 0$

|       | *x            | *у            |

|-------|---------------|---------------|

| Begin | A             | В             |

| 1     | A^B           | В             |

| 2     | A^B           | $(A^B)^B = A$ |

| 3     | $(A^B)^A = B$ | A             |

| End   | В             | A             |

### Two's Complement

## Range of integers

- A mathematical integer ranges from  $-\infty$  to  $+\infty$

- Consequently, a mathematical integer consists of an unbounded number of bits.

- No computer can store all the integers in this range (would require infinite storage).

- To use computer memory more efficiently, two broad categories of integer representation have been developed: unsigned integers and signed integers.

### Unsigned & signed integer arithmetic

• An unsigned integer ranges from 0 to  $+\infty$ .

The maximum unsigned integer that a computer can store depends on the number of bits the computer allocates to store an unsigned integer.

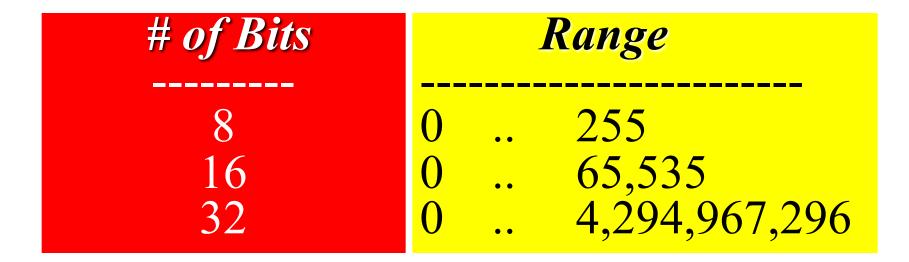

Range of unsigned integers

## Range of unsigned integers

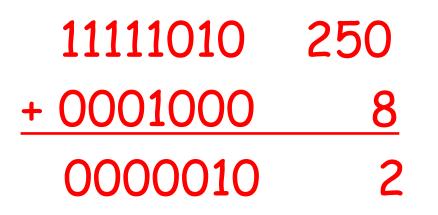

• Let's add 19 and 23  $1 \quad 111 \leftarrow carry$   $0 \quad 0 \quad 0 \quad 10 \quad 011 \quad 19$   $\underline{0 \quad 0 \quad 0 \quad 10111} \quad \underline{23}$  $0 \quad 0 \quad 10 \quad 1010 \quad 42$

Given an 8-bit allocation, what happens when we add 250 and 8

• The 1 bit that carries out of the left end of the operation will be discarded. The answer we compute will be 2, which is (250 + 8) modulo 256

## Range of unsigned integers

- The previous problem arises when you try to store a number that is not within the range defined by the allocation.

- With an 8-bit allocation, the largest number that can be stored is 255; however, the result of the addition is 258.

- Overflow is the term used for the condition that results when there are insufficient bits to represent a number in binary.

### Signed 8-bit arithmetic

- So far we have concentrated on positive numbers.

- There is no negative sign inside the computer; therefore, we have to devise a scheme for representing negative numbers.

- We will consider One's complement and two's complement.

- For simplicity, we will use an 8-bit representation.

### Signed 8-bit arithmetic

- One's complement format of a number

- Change the number to binary, ignoring the sign.

- Add Os to the left of the binary number to make a total of 8 bits

- If the sign is positive, no more action is needed.

- If the sign is negative, complement every bit (i.e. change from 0 to 1 or from 1 to 0)

Signed 8-bit arithmetic

- Write 25 in one's complement format

00011001

25 = (2<sup>4</sup> + 2<sup>3</sup> + 2<sup>0</sup>)

- Write -25 in one's complement format

- Since the number is negative, complement each bit

- 11100110 -25

### Signed 8-bit arithmetic

- One's complement

- Negation is easy.

- Addition / subtraction is relatively easy...

- Range:  $-(2^{n-1} 1)$  to  $+(2^{n-1} 1)$

- Drawback: Two values for 0

- +0 0000000

- -0 11111111

### One's Complement to Decimal

- If the sign bit (the leftmost bit) is 0, convert from binary to decimal.

- If the sign bit is 1 (negative number)

- complement the number

- convert the number to decimal

- put a negative sign in front of the number.

## One's Complement to Decimal

- Convert the following 1's complement representation to decimal:

- a) **1**1110001:

- Since the sign bit is 1, complement the number: 00001110

- Convert to decimal:  $00001110_2 = 14_{10}$

- Put a negative sign in front: -14

- b) 00011010

- Since the sign bit is 0, do not complement the number, just do the direct binary to decimal conversion.

- · 2<sup>4</sup> + 2<sup>3</sup> + 2<sup>1</sup> = 26

- Most computers today use 2's complement representation for negative numbers.

- The 2's complement of a negative number is obtained by adding 1 to the 1's complement.

- For -13:

- 00001101 base integer

- 11110010 1's complement

+1

11110011 2's complement

- Write -25 in two's complement format.

- +25 = 2<sup>4</sup> + 2<sup>3</sup> + 2<sup>0</sup> = 00011001

- Formats for -25 are:

- 11100110 one's complement

- 11100111 tv

- two's complement

To add two integers in two's complement, add two bits and propagate the carry to the next column. If there is a final carry after the leftmost column addition, discard it.

```

Add -25 and 20:

11100111 (-25)

<u>00010100 (20)</u>

11111011

```

- Since the negative of any number is its two's complement, the sum of a number and its two's complement is always 0

- The difference, a b, is computed as a + twos\_complement(b) (i.e., flip bits and add 1)

- Add +12 and -12

- $+12 = 00001100_{2}$

- $-12 = 11110100_2$

- 0 0000000<sub>2</sub>

### Summary: 2's complement

- Two's complement

- Negation is easy

- Addition / subtraction is easy

- One value for zero.

- Range:  $-(2^{n-1})$  to  $+(2^{n-1}-1)$

- Conversion:

- If the sign bit is 0, convert the binary number to decimal.

- If the sign bit is 1 subtract 1 from the binary number

- complement each bit

- convert the binary number to decimal

- put a minus sign in front

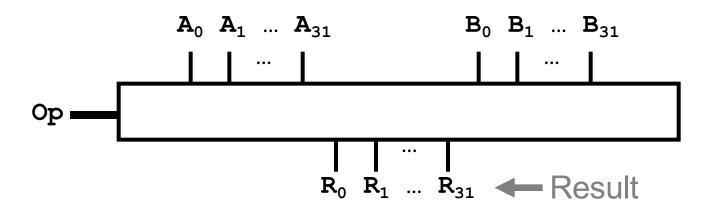

# Constructing an ALU

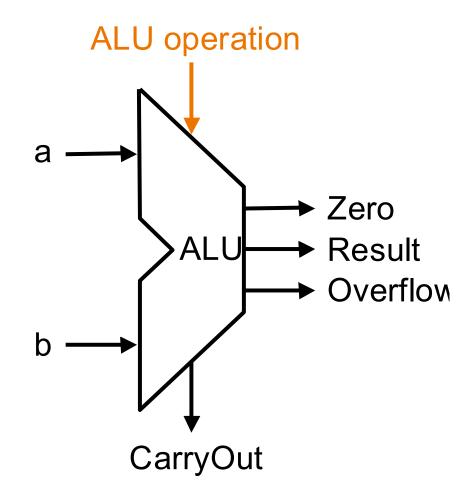

# Arithmetic Logic Unit

- The device that performs the arithmetic operations and logic operations.

- arithmetic ops: addition, subtraction

- logic operations: AND, OR

- For MIPS we need a 32 bit ALU

- can add 32 bit numbers, etc.

# Starting Small

- We can start by designing a 1 bit ALU.

- Put a bunch of them together to make larger ALUs.

- building a larger unit from a 1 bit unit is simple for some operations, can be tricky for others.

- Bottom-Up approach:

- build small units of functionality and put them together to build larger units.

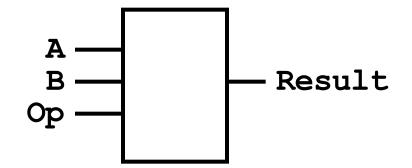

# 1 bit AND/OR machine

• We want to design a single box that can compute either AND or OR.

- We will use a *control input* to determine which operation is performed.

- Name the control "op".

- if Op==0 do an AND

- if Op==1 do an OR

### Truth Table For 1-bit AND/OR

| Op | A | В | Result |

|----|---|---|--------|

| 0  | 0 | 0 | 0      |

| 0  | 0 | 1 | 0      |

| 0  | 1 | 0 | 0      |

| 0  | 1 | 1 | 1      |

| 1  | 0 | 0 | 0      |

| 1  | 0 | 1 | 1      |

| 1  | 1 | 0 | 1      |

| 1  | 1 | 1 | 1      |

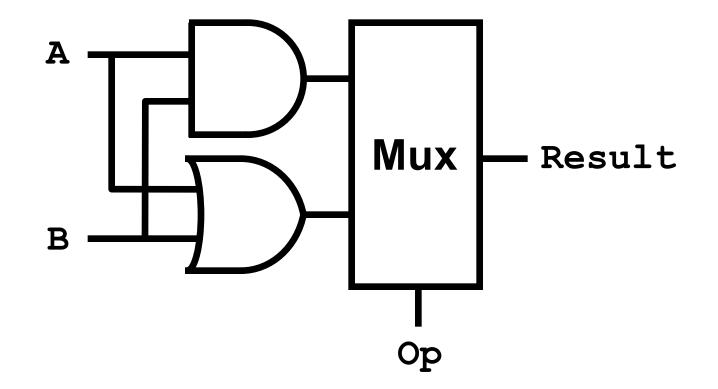

# Logic for 1-Bit AND/OR

- We could derive SOP or POS and build the corresponding logic.

- We could also just do this:

- Feed both A and B to an OR gate.

- Feed A and в to an AND gate.

- Use a 2-input MUX to pick which one will be used.

- Op is the selection input to the MUX.

### Logic Design for 1-Bit AND/OR

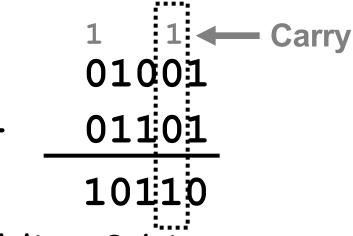

## Addition A painful reminder of the test

- We need to build a 1 bit adder

- compute binary addition of 2 bits.

- We already know that the result is 2 bits.

| A | В | <b>O</b> <sub>0</sub> | 0 <sub>1</sub> |

|---|---|-----------------------|----------------|

| 0 | 0 | 0                     | 0              |

| 0 | 1 | 0                     | 1              |

| 1 | 0 | 0                     | 1              |

| 1 | 1 | 1                     | 0              |

This is addition, not logical OR! A + B  $O_0 O_1$

## One Implementation

### Binary addition and our adder

#### 1 1 ← Carry 01001 01101 10110

- What we really want is something that can be used to implement the binary addition algorithm.

- $O_0$  is the carry

- $O_1$  is the sum

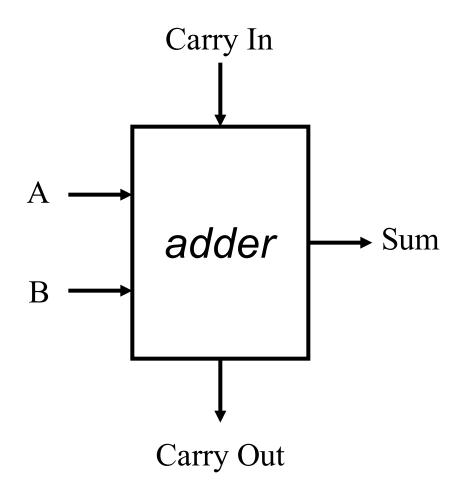

### What about the second column?

- We are adding 3 bits

- new bit is the carry from the first column.

- The output is still 2 bits, a *sum* and a *carry*

#### **Revised Truth Table for Addition**

| A | В | Carry | Carry | Sum |

|---|---|-------|-------|-----|

| _ |   | In    | Out   |     |

| 0 | 0 | 0     | 0     | 0   |

| 0 | 0 | 1     | 0     | 1   |

| 0 | 1 | 0     | 0     | 1   |

| 0 | 1 | 1     | 1     | 0   |

| 1 | 0 | 0     | 0     | 1   |

| 1 | 0 | 1     | 1     | 0   |

| 1 | 1 | 0     | 1     | 0   |

| 1 | 1 | 1     | 1     | 1   |

# Logic Design for new adder

- We can derive SOP expressions from the truth table.

- We can build a combinational circuit that implements the SOP expressions.

- We can put it in a box and give it a name.

### New Component: Adder

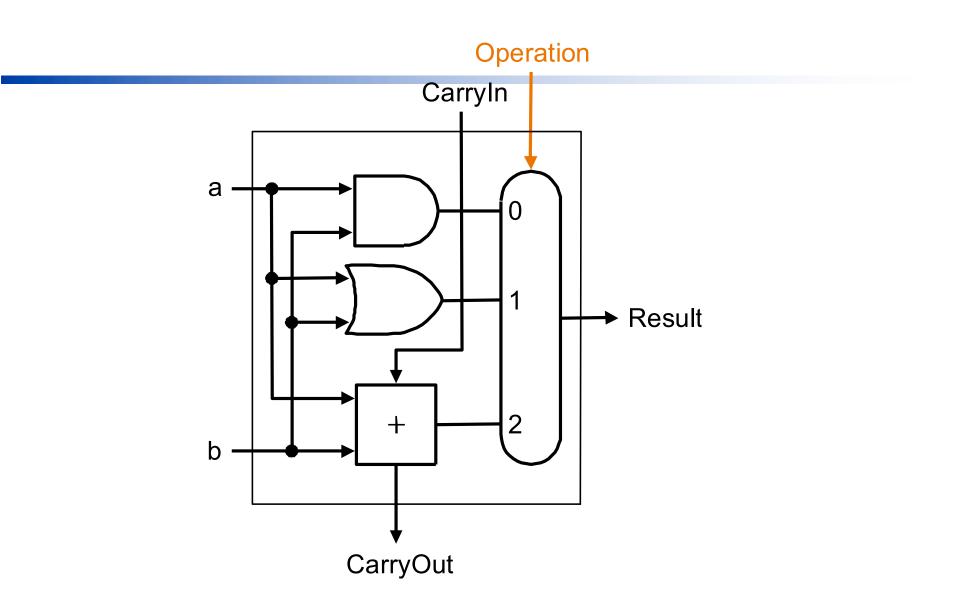

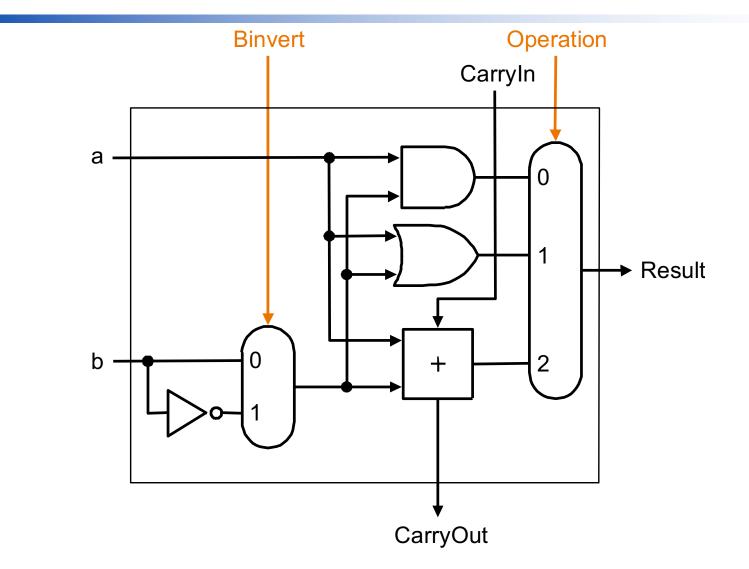

# 1 Bit ALU

- Combine the AND/OR with the adder.

- We must now use a 4-input MUX with 2 selection inputs.

#### AND OR add

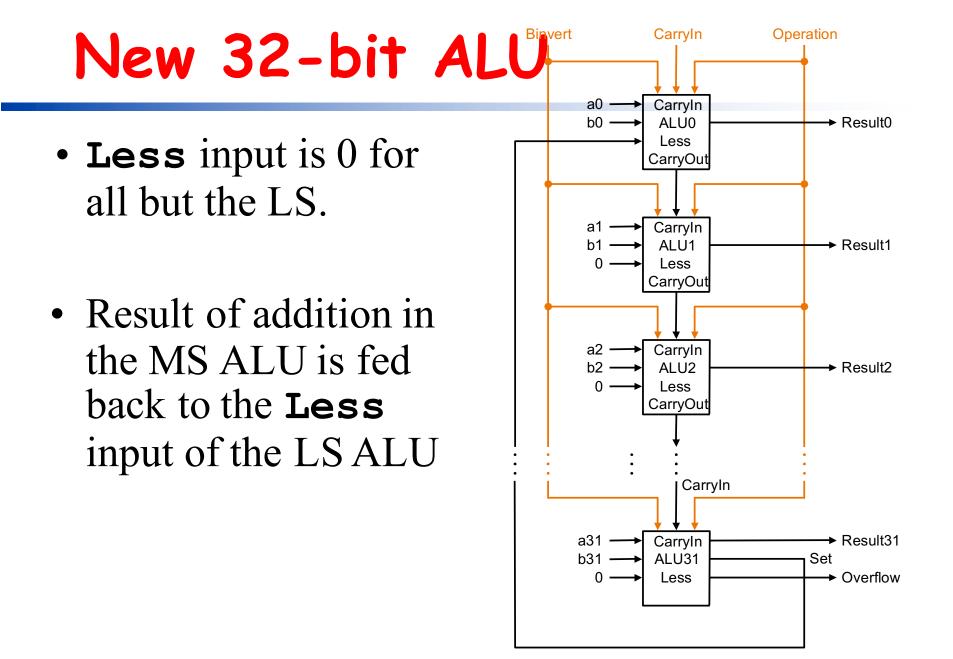

## Building a 32 bit ALU

- 64 inputs

- 3 different Operations (AND, OR, add).

- 32 bit output

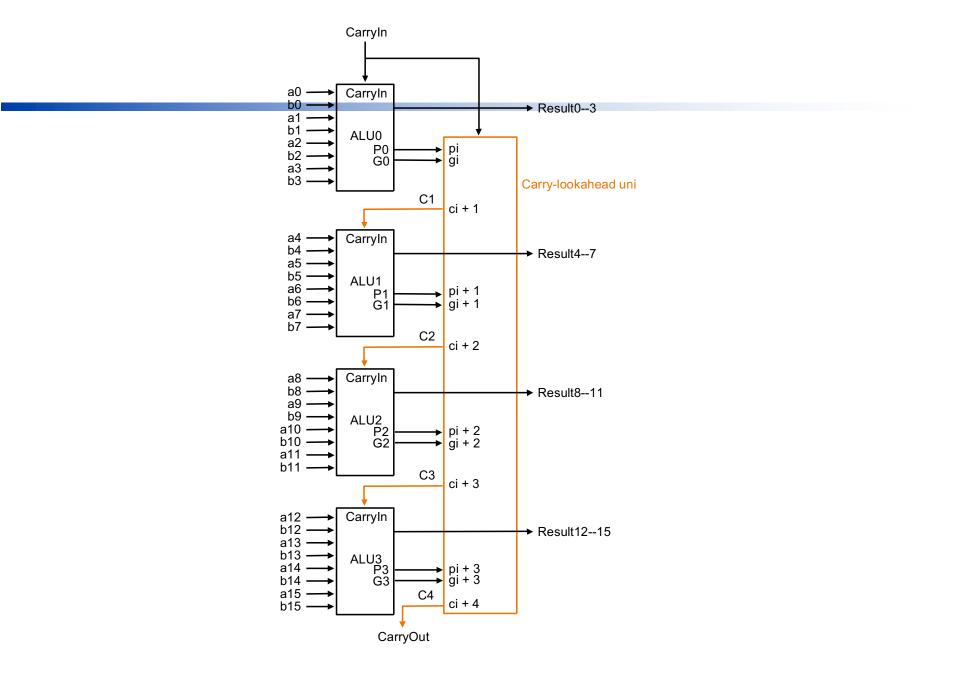

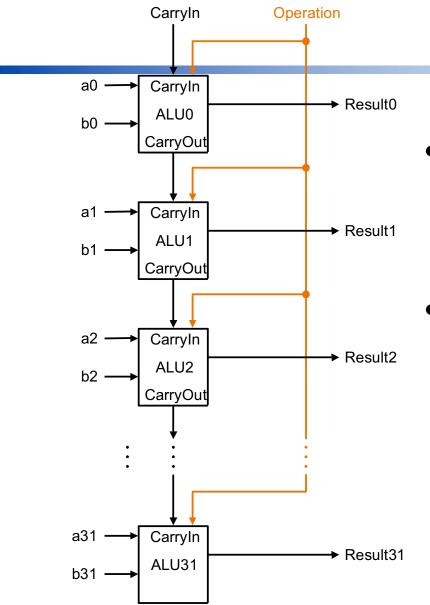

#### Ripple Carry Adder

- Carry out from ALU<sub>0</sub> is sent to carry in of ALU<sub>1</sub>

- How long will it take for the result to become available?

- the CarryOuts must propagate through all 32 1-Bit ALUs.

## New Operation: Subtraction

Subtraction can be done with an adder:

A - B can be computed as A + -B

- To negate B we need to:

- invert the bits.

- add 1

# Negating B in the ALU

- We can negate B by in the ALU by:

- providing B to the adder.

- need a selection bit to do this.

- To add 1, just set the initial carry in to 1!

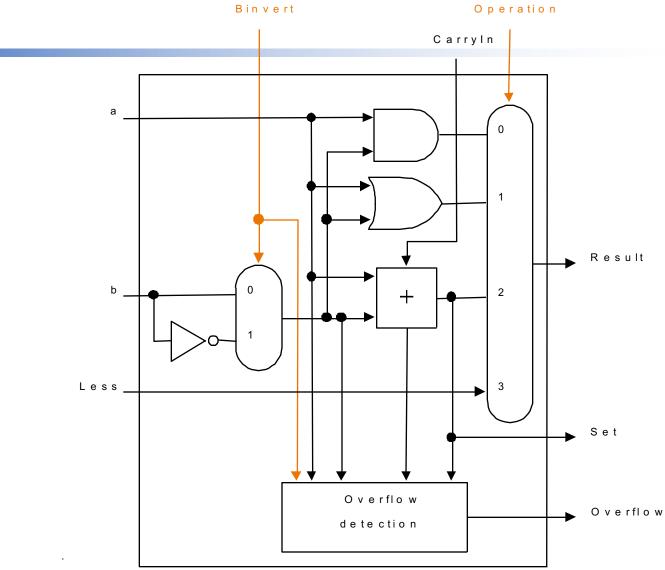

## Revised 1 Bit ALU

## Uses for our ALU

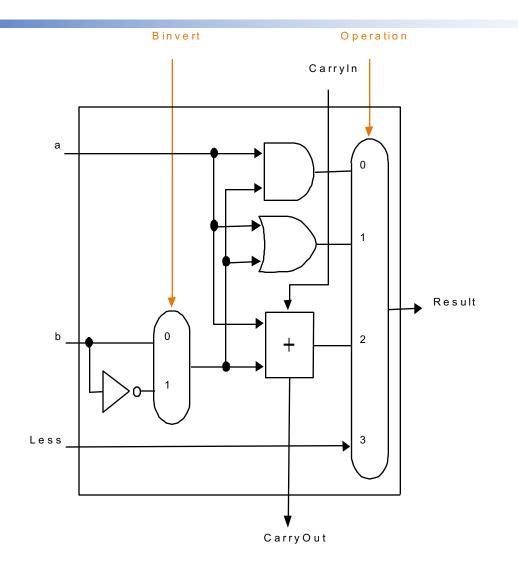

- addition, subtraction, OR and AND instructions can be implemented with our ALU.

- we still need to get the right values to the ALU and set control lines.

- We can also support the slt instruction.

- need to add a little more to the 1 bit ALU.

## Supporting slt

slt needs to compare 2 numbers.

comparison requires a subtraction.

if A-B is negative, then A<B is true. otherwise A<B is false.

True: output should be 0000000...001 False: output should be 0000000...000

# slt **Strategy**

- To compute slt A B:

- subtract B from A (set binvert and the L.S. Carry In to 1.

- Result for all 1-bit ALUs except the LS should always be 0.

- Result for the LS 1-bit ALU should be the result bit from the MS 1-bit ALU!

LS: Least significant (rightmost)

MS: Most significant (leftmost)

New 1-bit ALU

### MSB ALU

#### Put it in a box and give it a name

# Speed is important.

- Using a *ripple carry adder* the time it takes to do an addition is too long.

- each 1-bit ALU has something like 2 levels of gates.

- The input to the i<sup>th</sup> ALU includes an output from the i-1<sup>th</sup> ALU.

- For 32 bits we have something like 64 gate delays before the addition is complete.

## Strategies for speeding things up.

- We could derive the truth table for each of the 32 result bits as a function of 64 inputs.

- We know we can build SOP expressions for each and implement using 2 levels of gates.

- This might be a good test question!

- don't worry, you would need so much paper I couldn't carry the tests to class...

# A more realistic approach

- The problem is the *ripple*

- The last carry-in is takes a long time to compute.

- We can try to compute the carry-in bits as fast as possible

- this is called *carry lookahead*

- It turns out we can easily compute the carry-in bits much faster (but not in constant time).

# Carry In Analysis

- CarryIn<sub>i</sub> is an input to the i<sup>th</sup> 1 bit adder.

- CarryOut<sub>i-1</sub> is connected to CarryIn<sub>i</sub>

- We know about how to compute the CarryOuts

| A | в | Cary | Cary | Sum |

|---|---|------|------|-----|

|   |   | In   | Out  |     |

| 0 | 0 | 0    | 0    | 0   |

| 0 | 0 | 1    | 0    | 0   |

| 0 | 1 | 0    | 0    | 1   |

| 0 | 1 | 1    | 1    | 0   |

| 1 | 0 | 0    | 0    | 1   |

| 1 | 0 | 1    | 1    | 0   |

| 1 | 1 | 0    | 1    | 0   |

| 1 | 1 | 1    | 1    | 1   |

# **Computing Carry Bits**

- Carry  $In_0$  is an input to the adder.

- we don't compute this it's an input.

- CarryIn<sub>1</sub> depends on  $A_0$ ,  $B_0$  and CarryIn<sub>0</sub>:

$CarryIn_{1} = (B_{0} \cdot CarryIn_{0}) + (A_{0} \cdot CarryIn_{0}) + (A_{0} \cdot B_{0})$

$CarryIn_2 = (B_1 \cdot CarryIn_1) + (A_1 \cdot CarryIn_1) + (A_1 \cdot B_1)$

We can substitute for  $CarryIn_1$  and get this mess:

CarryIn<sub>2</sub> =

$$(B_1 \cdot B_0 \cdot CarryIn_0) + (B_1 \cdot A_0 \cdot CarryIn_0) + (B_1 \cdot A_0 \cdot B_0) + (A_1 \cdot B_0 \cdot CarryIn_0) + (A_1 \cdot A_0 \cdot B_0) + (A_1 \cdot B_0 \cdot CarryIn_0) + (A_1 \cdot A_0 \cdot B_0) + (A_1 \cdot B_1)$$

The size of these expressions will get too big (that's the whole problem!).

#### Another way to describe CarryIn

$$C_{i+1} = (B_i \cdot C_i) + (A_i \cdot C_i) + (A_i \cdot B_i)$$

=  $(A_i \cdot B_i) + (A_i + B_i) \cdot C_i$

$A_i \cdot B_i$ : Call this Generate (G<sub>i</sub>)  $A_i + B_i$ : Call this Propagate (P<sub>i</sub>)

$C_{i+1} = G_i + P_i \cdot C_i$

# Generate and Propagate

$C_{i+1} = G_i + P_i \bullet C_i$  $G_i = A_i \bullet B_i$  $P_i = A_i + B_i$

- When  $A_i$  and  $B_i$  are both 1,  $G_i$  becomes a 1.

- a CarryOut is generated.

- If P<sub>i</sub> is a 1, any Carry in is propagated to Carry Out.

# Using G<sub>i</sub> and P<sub>i</sub>

$$C_1 = G_0 + P_0 \cdot C_0$$

$$C_{2} = G_{1} + P_{1} \cdot C_{1}$$

=  $G_{1} + P_{1} \cdot (G_{0} + P_{0} \cdot C_{0})$

=  $G_{1} + P_{1} \cdot G_{0} + P_{1} \cdot P_{0} \cdot C_{0}$

$$C_3 = G_2 + P_2 \cdot G_1 + P_2 \cdot P_1 \cdot G_0 + P_2 \cdot P_1 \cdot P_0 \cdot C_0$$

# Implementation

- Expression still get too big to handle (for 32 bits).

- We can minimize the time needed to compute all the CarryIn bits for a 4 bit adder.

- Connect a bunch of 4 bit adders together and treat CarryIns to these adders in the same manner.